NAND闪存芯片利用3D堆叠技术成功解决体积压缩难题存储与灾备

堆叠式3D NAND芯片将在未来四年内成为闪存芯片市场上的主流方案。根据分析企业IHS的推测,这项新技术的出现将令当下闪存制造商们所大肆宣扬的芯片尺寸压缩方案变得黯然失色,并在未来成为削减产品尺寸、扩大产品容量的首先机制。

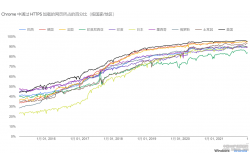

这家技术分析企业还就此制作了一份图表,其中显示3D NAND方案到2017年将占据超过三分之二的闪存市场份额——相比之下,目前其市场占有率仅为1%到2%。

全球3D NAND出货量在整体NAND闪存出货量当中所占比例(来源:HIS,2013年10月)

为什么会这样?简而言之:目前16到19纳米工艺已经是NAND闪存产品的极限,任何进一步压缩尺寸的尝试都会带来极高的成本且导致存储位不再稳定可靠。有鉴于此,要想在同样体积的闪存产品中获得更大存储空间,我们就必须往芯片里塞进更多闪存单元层。

三星公司于今年八月宣布,他们正在利用其V-NAND技术将3D堆叠方案变成现实。

IHS公司内存与存储高级分析师Dee Robinson在一份录音声明中这样解读上述图表:“目前大部分技术人员已经达成共识,NAND闪存再有一到两代产品就将逼近传统单导体技术的理论极限。随着光刻技术精度的进一步提升,产品的性能表现与可靠性将大幅退化。如此一来,NAND根本无法以足够低廉的成本广泛普及到各种应用领域。”

在芯片上进行存储层堆叠则不仅能够增加容量,更可能在未来将闪存产品的成本控制到较低水平。

HIS公司的分析人士也表示:“这很可能成为NAND进入新水平的最具成本效益的方式,因为大部分现有生产设备都能够与新产品顺利对接,这一方面能够最大限度减少开支、另一方面则有效提高了投资回报率。”不过需要指出的是,“由于堆叠式技术所使用的多级结构,故障分析工作会变得难于进行。”